A Utility for Converting State Diagrams into Synthesizable VHDL

Tom Mayo

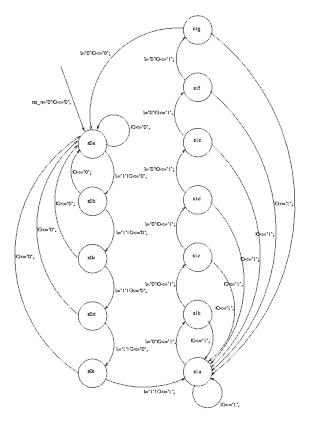

My master's thesis (PDF, 170 kB) (or cover (PDF, 12 kB), reconstructed contents (PDF, 20 kB), and body (PDF, 227 kB)) involved writing brusey20, a tool which converts state diagrams into synthesizable VHDL. After entering state diagrams with XFig, jfig or WinFIG, you run brusey20 on the exported .PIC file to yield a behavioral VHDL description of your state machine. This VHDL code is suitable for simulation or synthesis using just about any tool.

The zip archive contains a Linux binary and the source code for brusey20 in case you want to recompile it. Currently, there are makefiles included for MSDOS, SunOS, AIX, and Linux. Let me know if you get it to work on another platform!

Note: brusey20 is protected by the Gnu Public License (GPL).

News:

· Version 2.8 added new bison variables and functions to yy2vvv.sed to prevent duplicate symbols when linking.

· Version 2.7 updated contact information.

· Version 2.6 FOUND thanks to Michael Goldberg of Zenith! allows reset synchronization (-sr option). See examples/sr.

· Version 2.5 LOST! corrects a problem in printing default transitions.

· Version 2.4 corrects a problem with geometrically large input drawings.

· Version 2.3 allows prioritization of state transitions.

Download

· b20-28.zip (88 kB) The source code (and Linux binary) for brusey20.

Comments: tmayo1 at rochester.rr.com